Status: Tags: #cards/cmpt295/isa Links: Instruction Set Architecture (ISA)

MIPS

Principles

?

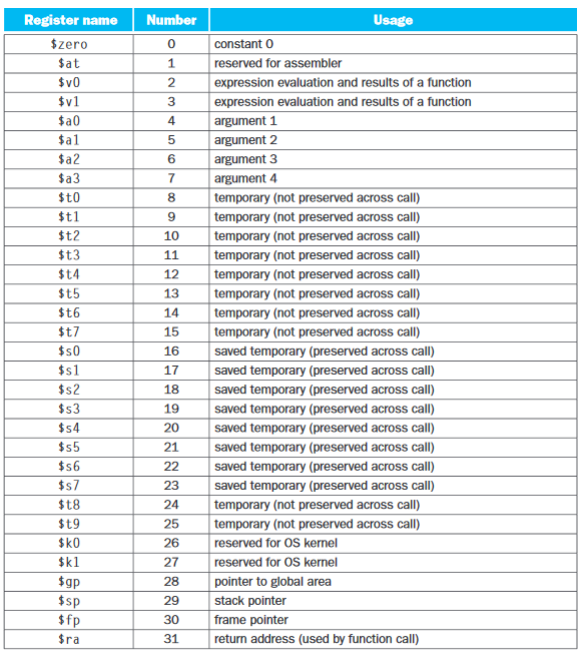

- 32 registers

- size of each register and word size is 32 bits

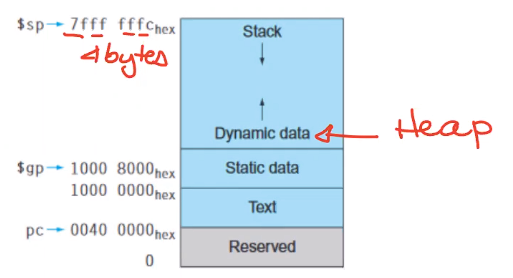

- size of memory adress is 32 bits

- Memory size is $2^32$ x 8

Registers

Memory Model

txregisters are not presrved, whilesxare

Instruction Set

- 3 operand assembly language

- Only having 3 operands for all instruction make microprocessor hardware easy

Instructions

lw reg, M

sw reg, M

add dest, a, b

sub dest, a, b

mul dest, a, b

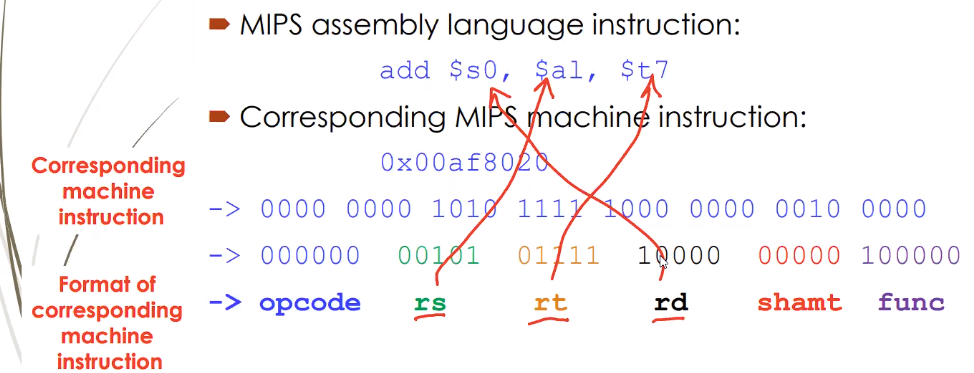

Example of Assembly to Machine

Layout

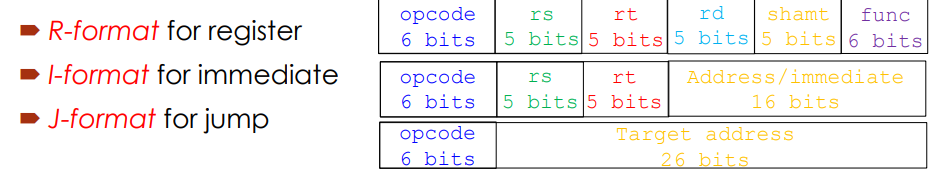

opcode ; operation of instruction (6)

rs ; first register (5)

rt ; second register source operand (5)

rd ; register destination operand (5)

shamt ; shift amount (6)

func ; function (code), variant of operation in opcode field

- 32 registers so 5 bits can help reach all indexes

Instruction Layouts

- opcode determines instruction + format of instruction to differentiate between the formats

Created:: 2022-03-15 19:59