Status: Tags: Links: Microprocessor

Microprocessor Staged Execution

Principles

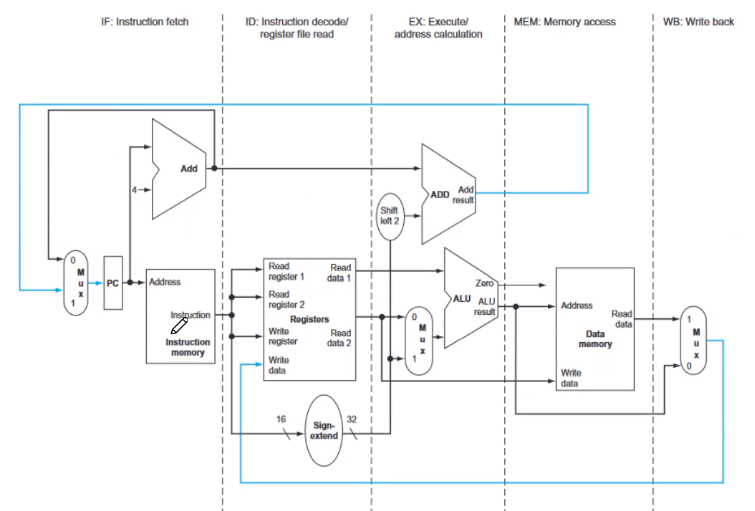

Structure

- Combinational logic circuit gets cut into 5 stages

- Each stage has a pipeline register in between to save intermediate values

- Invisible to us unlike PC

Diagram

Stages (FDEMW)

- Fetch

- Read instruction located at memory address in PC into instruction register

- Decode

- Decode instruction and read content of register operands (or implicit stack pointer register) from register file

- Execute

- Perform operation using ALU unit according to opcode, inc/dec rsp, compute effective address, set condition codes

- Memory

- Read/write data values from/to memory (memory-access instructions)

- Write back

- Write values from/to memory (memory-access instructions)

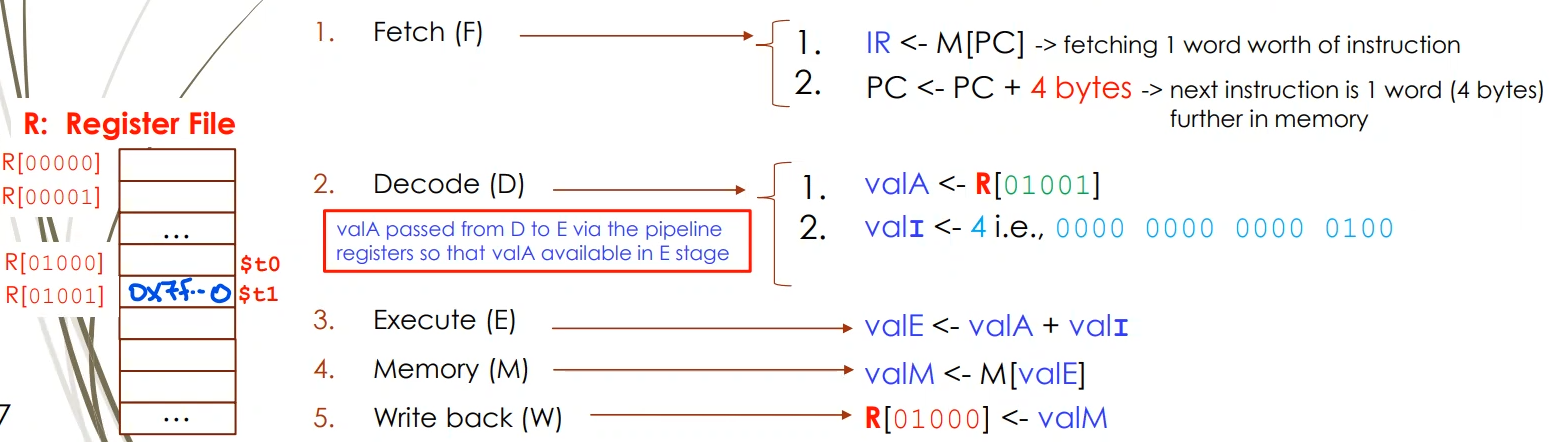

Example

Instruction

Process

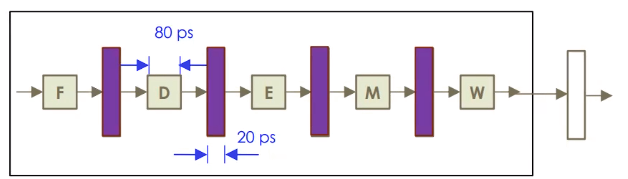

Analysis

- 80ps + 20s = 100ps

Latency

- 5(80) + 5(20) = 500ps

Throughput

- 1/500

Cycles per instruction (CPI)

- 5

References:

Created:: 2022-04-03 17:17